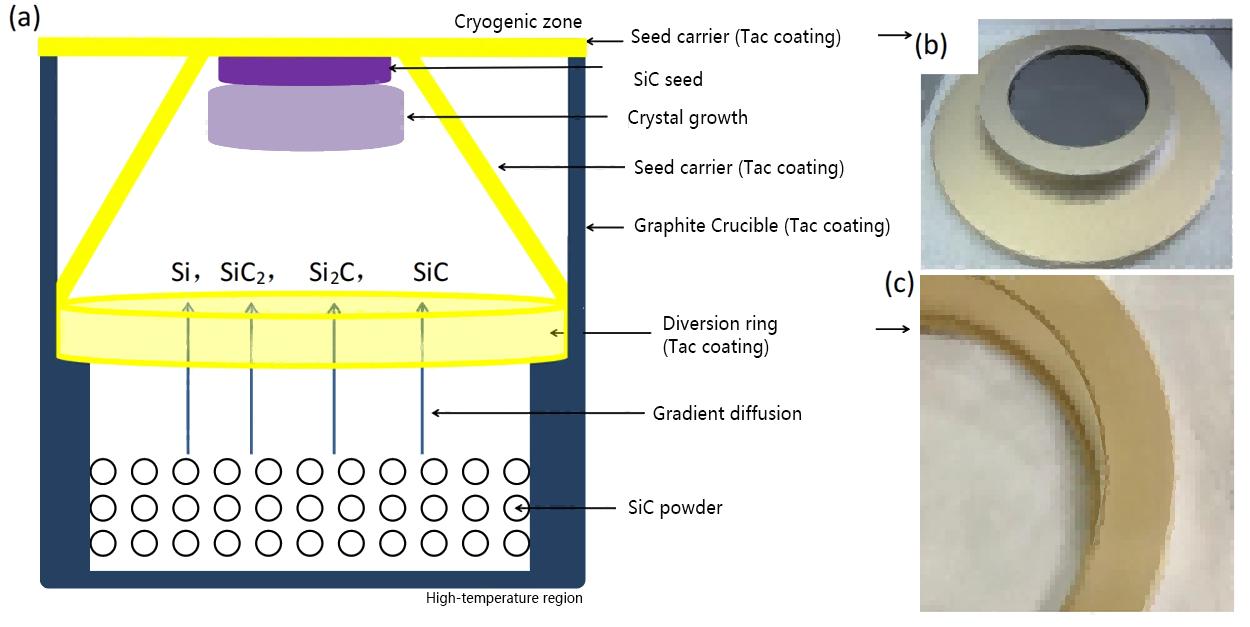

Semicera furnisce rivestimenti specializati di carburu di tantalu (TaC) per vari cumpunenti è trasportatori.U prucessu di rivestimentu di punta di Semicera permette à i rivestimenti di carburu di tantalu (TaC) per ottene una alta purezza, stabilità à alta temperatura è alta tolleranza chimica, migliurà a qualità di u produttu di cristalli SIC / GAN è strati EPI (Susceptor TaC rivestitu di grafite), è allargendu a vita di i cumpunenti chjave di u reattore. L'usu di u revestimentu di carburu di tantalu TaC hè di risolviri u prublema di u bordu è di migliurà a qualità di a crescita di cristalli, è Semicera hà avanzatu risolviu a tecnulugia di rivestimentu di carburu di tantalu (CVD), ghjunghje à u livellu avanzatu internaziunale.

U carburu di silicium (SiC) hè un materiale chjave in a terza generazione di semiconduttori, ma u so rendimentu hè statu un fattore limitante per a crescita di l'industria. Dopu à una larga prova in i laboratori di Semicera, hè statu trovu chì TaC sprayed è sinterizzati ùn manca a purità è uniformità necessaria. In cuntrastu, u prucessu CVD assicura un livellu di purità di 5 PPM è una uniformità eccellente. L'usu di CVD TaC migliora significativamente u rendimentu di i wafers di carburu di siliciu. Accoltamu discussioniAnelli à trè segmenti in grafite rivestite in TaC per riduce ulteriormente i costi di wafers SiC.

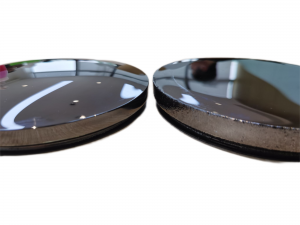

Dopu à anni di sviluppu, Semicera hà cunquistatu a tecnulugia diCVD TaCcù i sforzi cumuni di u dipartimentu R&D. I difetti sò faciuli fà accade in u prucessu di crescita di wafers SiC, ma dopu l'usuTaC, a diferenza hè significativa. Sottu hè un paraguni di wafers cù è senza TaC, oltri a parti Simicera 'per crescita single cristallu.

cù è senza TaC

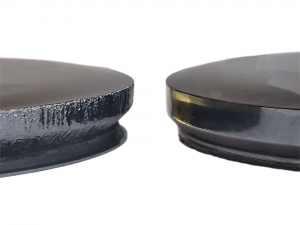

Dopu aduprà TaC (diritta)

In più, Semicera'sI prudutti rivestiti di TaCmostranu una vita di serviziu più longa è una resistenza à alta temperatura più granderivestimenti SiC.E misurazioni di laboratoriu anu dimustratu chì u nostrurivestimenti TaCpò esse realizatu in modu coerente à temperature finu à 2300 gradi Celsius per periodi estesi. Eccu alcuni esempi di i nostri campioni: