Campu d'applicazione

1. Circuit integratu high-vitezza

2. Dispositivi microwave

3. Circuit integratu High temperature

4. dispusitivi Power

5. Circuit integratu Low power

6. MEMS

7. Circuit integratu Low voltage

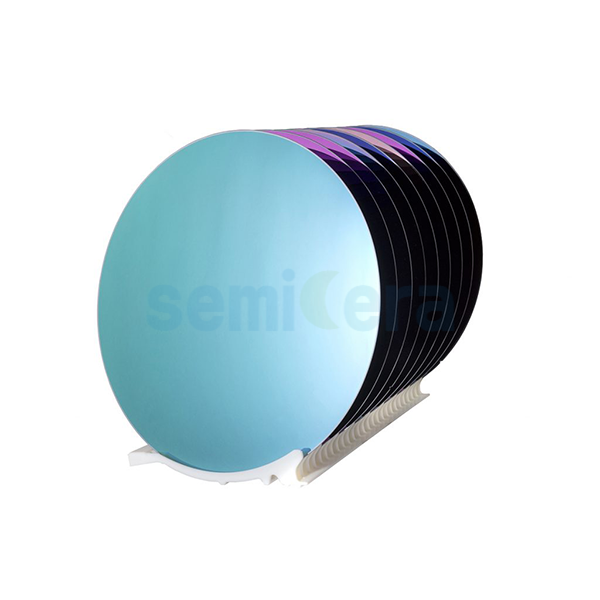

| Articulu | Argumentu | |

| In generale | Diametru di wafer | 50/75/100/125/150/200mm ± 25um |

| Arcu / Warp | <10um | |

| Particelle | 0.3um <30ea | |

| Flats/Notch | Flat o Notch | |

| Exclusion Edge | / | |

| Layer di u dispusitivu | Device-layer Type/Dopant | N-Type/P-Type |

| Orientazione di u dispusitivu | <1-0-0> / <1-1-1> / <1-1-0> | |

| Spessore di u dispusitivu | 0.1 ~ 300um | |

| Resistività di u dispusitivu | 0.001 ~ 100.000 ohm-cm | |

| Particelle di u dispusitivu | <30ea@0.3 | |

| Device Layer TTV | <10um | |

| Device Layer Finish | Pulitu | |

| BOX | Spessore di l'ossidu termale enteratu | 50nm (500Å) ~ 15um |

| Maniglia Layer | Maniglia Tipu Wafer / Dopant | N-Type/P-Type |

| Manipulu l'Orientazione di Wafer | <1-0-0> / <1-1-1> / <1-1-0> | |

| Maneggiare a resistenza di wafer | 0.001 ~ 100.000 ohm-cm | |

| Spessore di Wafer di maniglia | > 100 um | |

| Maniglia Wafer Finish | Pulitu | |

| I wafers SOI di specificazioni di destinazione ponu esse persunalizati secondu e esigenze di i clienti. | ||

-

Sabbia di quartz

-

Anneau en graphite recouvert de carbure de tantale

-

Susceptor di crescita di cristalli rivestiti di carburu di silicium

-

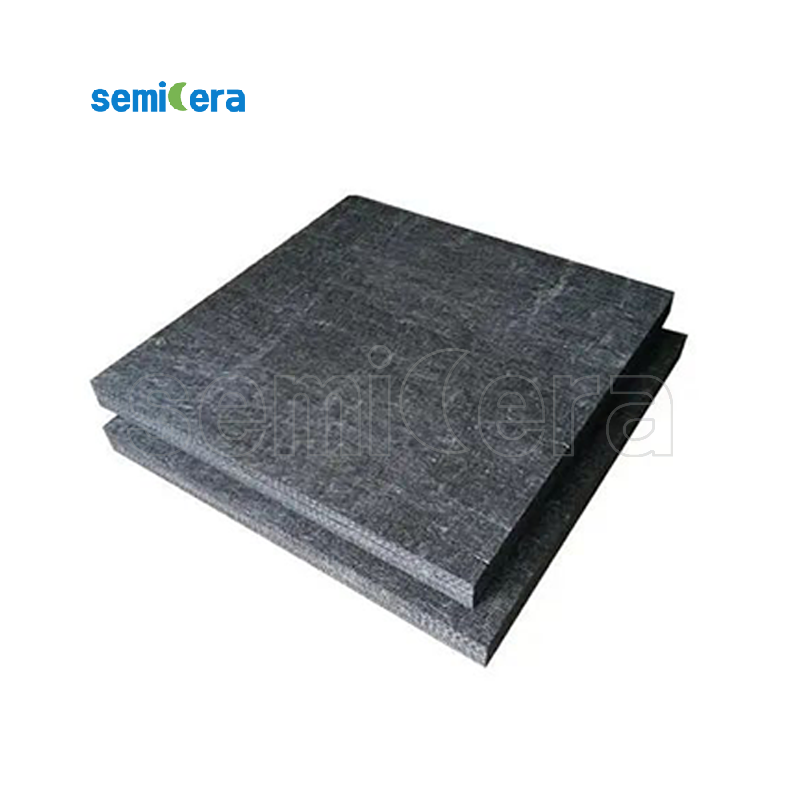

Materiale di grafite d'alta densità in feltro duru di grafite

-

Carbure de silicium résistant à la corrosion Efficacité céramique...

-

Pagaie en carbure de silicium de haute pureté