U Wafer di Silicon On Insulator (SOI) di Semicera hè in prima linea di l'innuvazione di i semiconduttori, offre un isolamentu elettricu rinfurzatu è prestazioni termiche superiori. A struttura SOI, custituita da una fina capa di siliciu nantu à un sustrato insulante, furnisce benefici critichi per i dispositi elettronichi d'altu rendiment.

I nostri wafer SOI sò pensati per minimizzà a capacità parassita è i correnti di fuga, chì hè essenziale per u sviluppu di circuiti integrati à alta velocità è bassa putenza. Sta tecnulugia avanzata assicura chì i dispositi operanu in modu più efficau, cù una velocità mejorata è un cunsumu d'energia ridutta, cruciali per l'elettronica muderna.

I processi di fabricazione avanzati impiegati da Semicera guarantiscenu a produzzione di wafer SOI cun uniformità è coerenza eccellenti. Questa qualità hè vitale per l'applicazioni in telecomunicazioni, automotive è elettronica di cunsumu, induve sò richiesti cumpunenti affidabili è d'altu rendiment.

In più di i so benefici elettrici, i wafers SOI di Semicera offrenu un insulamentu termale superiore, rinfurzendu a dissipazione di u calore è a stabilità in i dispositi d'alta densità è d'alta putenza. Questa funzione hè particularmente preziosa in l'applicazioni chì implicanu una generazione significativa di calore è necessitanu una gestione termica efficace.

Scegliendu u Silicon On Insulator Wafer di Semicera, investite in un pruduttu chì sustene l'avanzamentu di e tecnulugia di punta. U nostru impegnu à a qualità è l'innuvazione assicura chì i nostri wafers SOI rispondenu à e rigorose esigenze di l'industria di i semiconduttori di l'oghje, fornendu a basa per i dispositi elettronici di prossima generazione.

| Articuli | Pruduzzione | Ricerca | Dummy |

| Parametri Crystal | |||

| Politipu | 4H | ||

| Errore di orientazione di a superficia | <11-20>4 ± 0,15 ° | ||

| Parametri elettrici | |||

| Dopantu | Nitrogenu di tipu n | ||

| Resistività | 0,015-0,025 ohm·cm | ||

| Parametri meccanichi | |||

| Diamitru | 150,0 ± 0,2 mm | ||

| Spessore | 350±25 μm | ||

| Orientazione pianu primaria | [1-100] ± 5 ° | ||

| Lunghezza piatta primaria | 47,5 ± 1,5 mm | ||

| Pianu secundariu | Nimu | ||

| TTV | ≤5 μm | ≤ 10 μm | ≤15 μm |

| LTV | ≤3 μm (5mm*5mm) | ≤5 μm (5mm*5mm) | ≤10 μm (5mm*5mm) |

| arcu | -15μm ~ 15μm | -35μm ~ 35μm | -45μm ~ 45μm |

| Warp | ≤ 35 μm | ≤45 μm | ≤55 μm |

| Rugosità frontale (Si-face) (AFM) | Ra≤0.2nm (5μm*5μm) | ||

| Struttura | |||

| Densità di micropipe | <1 ea/cm2 | <10 ea/cm2 | <15 ca/cm2 |

| impurità metalliche | ≤5E10atomi/cm2 | NA | |

| BPD | ≤1500 ea/cm2 | ≤3000 ea/cm2 | NA |

| TSD | ≤500 ca/cm2 | ≤1000 ea/cm2 | NA |

| Qualità Frontale | |||

| Fronte | Si | ||

| Finitura di a superficia | Si-face CMP | ||

| Particelle | ≤60ea/wafer (taglia ≥0.3μm) | NA | |

| Scratchs | ≤5ea/mm. Lunghezza cumulativa ≤Diametru | Lunghezza cumulativa ≤2 * Diametru | NA |

| Buccia d'arancia / buche / macchie / striature / crepe / contaminazione | Nimu | NA | |

| Chips di bordu / indentazioni / frattura / piastre esagonali | Nimu | ||

| Zone polytype | Nimu | Area cumulativa ≤ 20% | Area cumulativa ≤ 30% |

| Marcatura laser frontale | Nimu | ||

| Back Quality | |||

| Finitura di daretu | C-face CMP | ||

| Scratchs | ≤5ea/mm, Lunghezza cumulativa ≤2 * Diametru | NA | |

| Difetti in daretu (chips di bordu / indentazioni) | Nimu | ||

| Rugosità di u spinu | Ra≤0.2nm (5μm*5μm) | ||

| Marcatura laser posteriore | 1 mm (da u bordu superiore) | ||

| Edge | |||

| Edge | Smusso | ||

| Imballaggio | |||

| Imballaggio | Epi-ready cun imballaggio in vacuum Imballaggio di cassette multi-wafer | ||

| *Note: "NA" significa senza dumanda Articuli micca citati ponu riferite à SEMI-STD. | |||

-

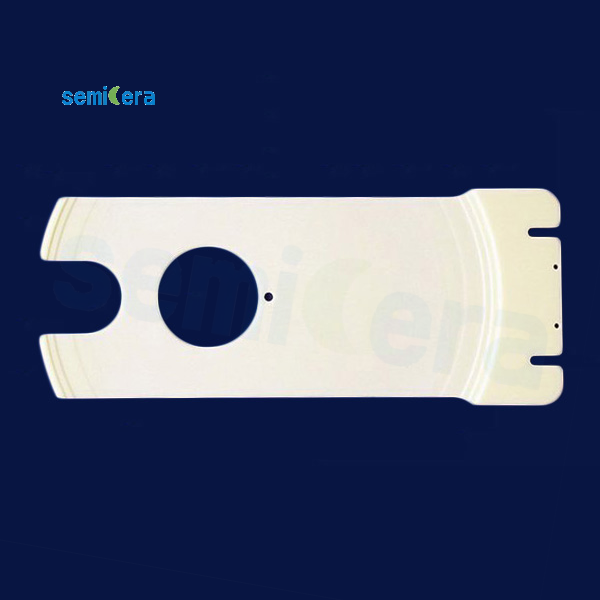

Forchetta ceramica semiconductora di zirconia

-

SiC Coating Graphite Wafer Susceptor

-

Barca in wafer di carburu di siliciu di qualità premium per Cr...

-

Barca in wafer di carburu di siliciu

-

Furnace à vacuum Riscaldatore Elettricu di Grafite Personalizatu

-

Suscetteur à barillet recouvert de carbure de silicium