1.About Circuits Integrati

1.1 U cuncettu è a nascita di circuiti integrati

Circuit integratu (IC): si riferisce à un dispositivu chì combina i dispositi attivi cum'è transistori è diodi cù cumpunenti passivi, cum'è resistori è capacitori, attraversu una seria di tecniche di trasfurmazioni specifiche.

Un circuitu o sistema chì hè "integratu" in un semiconductor (cum'è siliciu o cumposti cum'è l'arsenidu di galliu) wafer secondu certe interconnessioni di circuiti è dopu imballatu in una cunchiglia per eseguisce funzioni specifiche.

In u 1958, Jack Kilby, chì era rispunsevuli di a miniaturizazione di l'equipaggiu elettronicu in Texas Instruments (TI), prupone l'idea di circuiti integrati:

"Siccomu tutti i cumpunenti cum'è capacitors, resistors, transistors, etc. ponu esse fatti da un materiale, pensu chì saria pussibule di fà nantu à un pezzu di materiale semiconductor è dopu interconnetta per furmà un circuitu cumpletu".

U 12 di settembre è u 19 di settembre di u 1958, Kilby hà finitu a fabricazione è a dimustrazione di l'oscillatore è u trigger di fasa, rispettivamente, marcatu a nascita di u circuit integratu.

In u 2000, Kilby hè stata premiata u Premiu Nobel in Fisica. U Cumitatu di u Premiu Nobel hà dettu una volta chì Kilby "hà stabilitu a fundazione per a tecnulugia di l'informatica muderna".

A stampa sottu mostra Kilby è u so brevettu di circuit integratu:

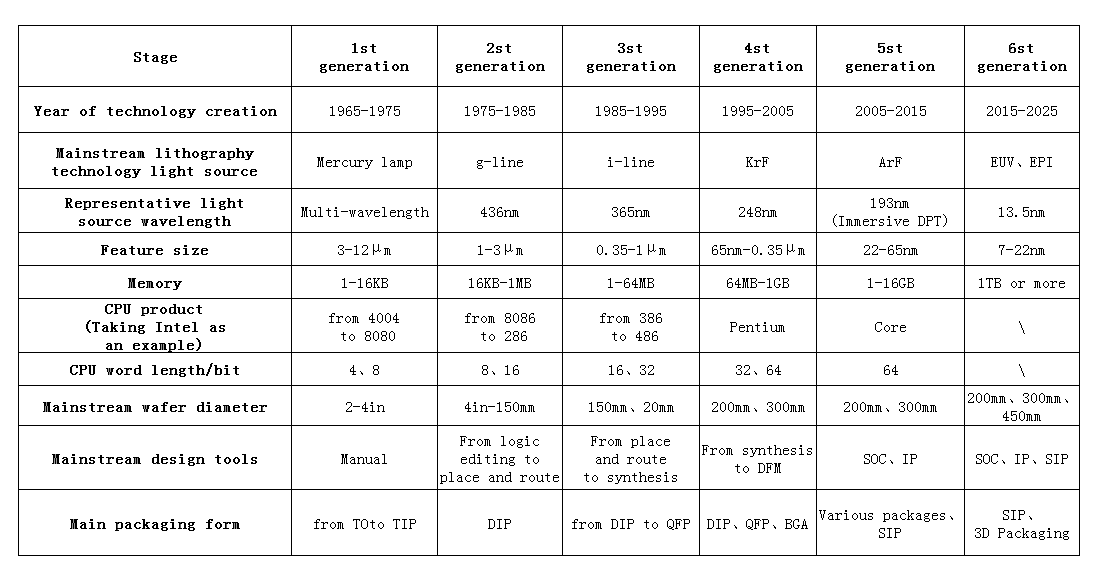

1.2 Sviluppu di tecnulugia di fabricazione di semiconductor

A figura seguente mostra e fasi di sviluppu di a tecnulugia di fabricazione di semiconduttori:

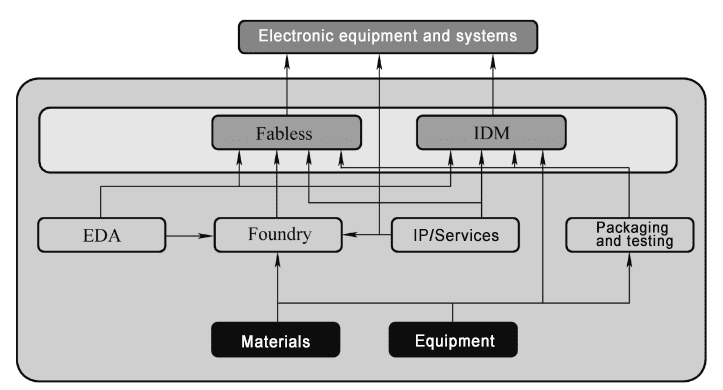

1.3 Circuit Integrated Industry Chain

A cumpusizioni di a catena di l'industria di i semiconduttori (principalmente circuiti integrati, cumprese i dispositi discreti) hè mostrata in a figura sopra:

- Fabless: Una cumpagnia chì cuncepisce prudutti senza una linea di produzzione.

- IDM: Integrated Device Manufacturer, fabricatore di dispositivi integrati;

- IP: Fabbricante di moduli di circuitu;

- EDA: Disegnu Elettronicu Automaticu, automatizazione di cuncepimentu elettronicu, a cumpagnia furnisce principalmente strumenti di cuncepimentu;

- Fonderia; Fonderia di wafer, chì furnisce servizii di fabricazione di chip;

- Imballaggi è teste di cumpagnie di fonderia: serve principalmente Fabless è IDM;

- Cumpagnia di materiali è attrezzature speciali: furnisce principalmente i materiali è l'equipaggiu necessarii per l'imprese di fabricazione di chip.

I prudutti principali pruduciuti cù a tecnulugia di semiconductor sò circuiti integrati è dispusitivi semiconductor discreti.

I prudutti principali di circuiti integrati include:

- Parti standard specifiche per l'applicazione (ASSP);

- Unità di microprocessore (MPU);

- Memoria

- Circuit integratu specificu di l'applicazione (ASIC);

- Circuitu Analogicu;

- Circuitu logicu generale (Circuit logicu).

I prudutti principali di i dispositi discreti semiconduttori includenu:

- Diode;

- Transistor;

- Dispositivu di putenza;

- Dispositivu d'alta tensione;

- Dispositivu à microonde;

- Optoelettronica;

- Dispositiu sensoru (Sensor).

2. Prucessu Manufacturing Circuit Integrated

2.1 Fabricazione di chip

Decine o ancu decine di millaie di chips specifichi ponu esse fatte simultaneamente nantu à una wafer di siliciu. U numaru di chips nantu à una wafer di siliciu dipende da u tipu di pruduttu è a dimensione di ogni chip.

I wafers di silicone sò generalmente chjamati sustrati. U diametru di i wafers di siliciu hè cresciutu annantu à l'anni, da menu di 1 inch à l'iniziu à i 12 inch cumunimenti usati (circa 300 mm) avà, è hè in una transizione à 14 inch o 15 inch.

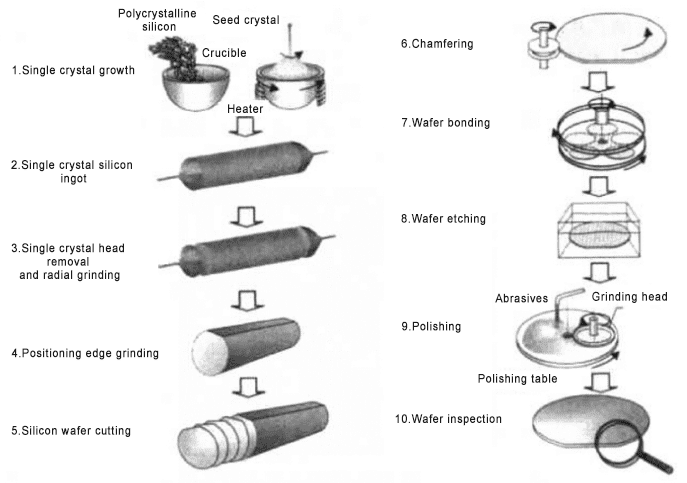

A fabricazione di chip hè generalmente divisa in cinque fasi: preparazione di wafer di silicium, fabricazione di wafer di silicium, test / scelta di chip, assemblea è imballaggio, è teste finali.

(1)

Preparazione di wafer di silicone:

Per fà a materia prima, u siliciu hè estrattu da a sabbia è purificatu. Un prucessu speciale pruduce lingotti di siliciu di diametru adattatu. I lingotti sò poi tagliati in sottili wafers di silicone per fà microchips.

I wafers sò preparati à specificazioni specifiche, cum'è i requisiti di u bordu di registrazione è i livelli di contaminazione.

(2)Produzione di wafer di siliciu:

Cunnisciuta ancu com'è a fabricazione di chip, a wafer di siliciu nuda arriva à a pianta di fabricazione di wafer di siliciu è poi passa per varii passaggi di pulizia, furmazione di film, fotolitografia, incisione è doping. U wafer di siliciu processatu hà un inseme cumpletu di circuiti integrati permanentemente incisi nantu à u wafer di siliciu.

(3)Prova è selezzione di wafers di silicone:

Dopu chì a fabricazione di wafer di siliciu hè finita, i wafers di siliciu sò mandati à l'area di prova / sorte, induve i chip individuali sò sondati è pruvati elettricamente. I patatine fritte accettabili è inaccettabili sò allora sorte, è i chips difetti sò marcati.

(4)Assemblage è imballaggio:

Dopu a prova / classificazione di wafers, i wafers entranu in u passu di l'assemblea è di l'imballa per imballà i chips individuali in un pacchettu di tubu protettivu. A parte posteriore di l'ostia hè in terra per riduce u gruixu di u sustrato.

Un film plasticu grossu hè attaccatu à u spinu di ogni wafer, è dopu una lama di sega in punta di diamante hè aduprata per separà i chips nantu à ogni wafer longu à e linee di scribe in a parte frontale.

U film plasticu nantu à u spinu di u wafer di siliciu mantene u chip di siliciu da cascà. In a pianta di assemblea, i boni chips sò pressati o evacuati per furmà un pacchettu di assemblea. In seguitu, u chip hè stampatu in una cunchiglia plastica o ceramica.

(5)Test finale:

Per assicurà a funziunalità di u chip, ogni circuitu integratu imballatu hè testatu per risponde à i requisiti di parametri elettrici è ambientali di u fabricatore. Dopu a prova finale, u chip hè mandatu à u cliente per l'assemblea in un locu dedicatu.

2.2 Divisione di Prucessu

I prucessi di fabricazione di circuiti integrati sò generalmente divisi in:

Front-end: U prucessu di front-end in generale si riferisce à u prucessu di fabricazione di dispusitivi cum'è transistors, cumpresi principalmente i prucessi di furmazione di isolamentu, struttura di porta, fonte è drenu, buchi di cuntattu, etc.

Back-end: U prucessu di back-end si riferisce principarmenti à a furmazione di linee di interconnessione chì ponu trasmette segnali elettrici à parechji dispositi nantu à u chip, cumpresu principalmente prucessi cum'è a deposizione dielettrica trà e linee di interconnessione, a furmazione di linea di metalli è a furmazione di pad di piombo.

Mid-stage: In ordine à migliurà u funziunamentu di transistors, nodes ticnoluggìa dâ avanzata dopu à 45nm / 28nm aduprà high-k dielectrics porta è prucessi di porta di metallu, è aghjunghje prucessi porta di sustituzione è prucessi interconnect lucale dopu à a surgente transistor è struttura drain hè preparatu. Sti prucessi sò trà u prucessu di front-end è u prucessu di back-end, è ùn sò micca usati in i prucessi tradiziunali, cusì sò chjamati prucessi mid-stage.

Di solitu, u prucessu di preparazione di u pirtusu di cuntattu hè a linea di divisione trà u prucessu di front-end è u prucessu di back-end.

Fora di cuntattu: un pirtusu incisu verticalmente in u wafer di siliciu per cunnette a linea di interconnessione metallica di u primu stratu è u dispusitivu di sustrato. Hè pienu di metallu cum'è tungstenu è hè adupratu per guidà l'elettrodu di u dispusitivu à a strata di interconnessione metallica.

Attraversu Hole: Hè u percorsu di cunnessione trà dui strati adiacenti di e linee di interconnessione di metalli, situati in a strata dielettrica trà i dui strati di metalli, è in generale hè pienu di metalli cum'è u ramu.

In un sensu largu:

Prucessu front-end: In un sensu largu, a fabricazione di circuiti integrati deve ancu include teste, imballaggio è altri passi. In cunfrontu cù a prova è l'imballu, a fabricazione di cumpunenti è interconnessioni sò a prima parte di a fabricazione di circuiti integrati, chjamati cullettivamente processi front-end;

Prucessu back-end: Testing è imballaggio sò chjamati prucessi back-end.

3. Appendice

SMIF: Interfaccia Meccanica Standard

AMHS: Sistema Automatizatu di Manutenzione di Materiale

OHT: Trasferimentu di Parancu Aereo

FOUP: Pod unificato con apertura frontale, esclusiva per wafer da 12 pollici (300 mm)

A più impurtante,Semicera pò furnisceparti di grafite, feltru molle/rigidu,parti di carburu di siliciu, Parti in carburu di siliciu CVD, èParti rivestite di SiC/TaCcù u prucessu di semiconductor pienu in 30 ghjorni.Aspittemu sinceramente à diventà u vostru cumpagnu à longu andà in Cina.

Tempu di post: Aug-15-2024